**TLE4208G**

Quad Half-Bridge Driver IC

تهيهوتوزيعقطعات

Data Sheet

Rev. 1.4, 2016-02-02

**Automotive Power**

### **Table of Contents**

# **Table of Contents**

| 1                          | Overview                                                                                                                                   |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 2                          | Block Diagram                                                                                                                              |

| <b>3</b><br>3.1<br>3.2     | Pin Configuration       0         Pin Assignment       0         Pin Definitions and Functions       0                                     |

| 4.1<br>4.2<br>4.3<br>4.3.1 | General Product Characteristics6Absolute Maximum Ratings8Functional Range9General Electrical Characteristics10Electrical Characteristics10 |

| 5<br>6                     | Application Information                                                                                                                    |

| 7                          | Revision History                                                                                                                           |

# 1-A Quad Half-Bridge Driver IC

**TLE4208G**

## 1 Overview

#### **Features**

- Driver for up to 3 motors

- Delivers up to 0.8 A continuous

- Optimized for DC motor management applications

- · Very low current consumption in stand-by (Inhibit) mode

- Low saturation voltage; typ.1.2 V total @ 25 °C; 0.4 A

- · Output protected against short circuit

- Error flag diagnosis

- Overvoltage lockout and diagnosis

- Undervoltage lockout

- CMOS/TTL compatible inputs with hysteresis

- No crossover current

- · Internal clamp diodes

- Overtemperature protection with hysteresis and diagnosis

- Enhanced power DSO-Package

- Green Product (RoHS compliant)

- AEC Qualified

PG-DSO-28

#### **Description**

The TLE4208G is a protected Quad-Half-Bridge-Driver designed specially for automotive and industrial motion control applications. The part is built using Infineous bipolar high voltage power technology DOPL.

In a cascade configuration up to three actuators (DC motors) can be connected between the four half-bridges. These four half-bridges are configured as 2 dual-half-bridges, which are supplied and controlled separately. Operation modes forward (cw), reverse (ccw), brake and high impedance are invoked from a standard interface.

The standard enhanced power PG-DSO-28 package meets the application requirements and saves PCB-board space and costs. Moreover the package is RoHS compliant.

Furthermore the built-in features like diagnosis, over- and undervoltage-lockout, short-circuit protection, overtemperature protection and the very low quiescent current in stand-by mode will open a wide range of automotive and industrial applications.

| Туре     | Package   | Marking  |

|----------|-----------|----------|

| TLE4208G | PG-DSO-28 | TLE4208G |

Data Sheet 3 Rev. 1.4, 2016-02-02

**Block Diagram**

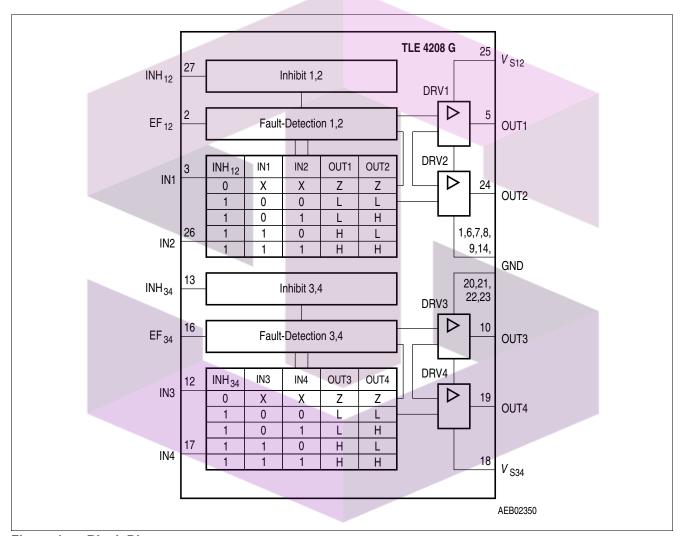

# 2 Block Diagram

Figure 1 Block Diagram

# **Input Logic**

Table 1 Functional Truth Table of Halfbridge 1 and 2

| INH <sub>12</sub> | IN1 | IN2      | OUT1  | OUT2 | MODE     |

|-------------------|-----|----------|-------|------|----------|

| 0                 | X   | X        | Z     | Z    | Stand-by |

| 1                 | 0   | 0        | L     | L    | Brake LL |

| 1                 | 0   | 1 ** 1 0 | 400 c | H    | CW       |

| 1                 | 1   | 0        | Н     |      | CCW      |

| 1                 | 1   | 1        | Н     | Н    | Brake HH |

Note: Half-Bridge 1 and 2 connected to a full-bridge

**Block Diagram**

Table 2 Functinal Truth Table of Halfbridge 3 and 4

| INH <sub>34</sub> | IN3 | IN4 | OUT3 | OUT4 | MODE     |

|-------------------|-----|-----|------|------|----------|

| 0                 | X   | X   | Z    | Z    | Stand-by |

| 1                 | 0   | 0   | L    | L    | Brake LL |

| 1                 | 0   | 1   | L    | Н    | CW       |

| 1                 | 1   | 0   | Н    | L    | CCW      |

| 1                 | 1   | 1   | Н    | Н    | Brake HH |

#### IN:

0 = Logic LOW

1 = Logic HIGH

X = Don't Care

# OUT:

Z = Output in tristate condition

L = Output in sink condition

X = Output in source condition

Note: Half-Bridge 3 and 4 connected to a full-bridge

Table 3 Diagnosis

| EF <sub>12</sub> EF <sub>34</sub> |   | Error                                      |  |  |  |  |  |  |

|-----------------------------------|---|--------------------------------------------|--|--|--|--|--|--|

| 1                                 | 1 | no error                                   |  |  |  |  |  |  |

| 0                                 | 1 | over temperature of half-bridge 1 and 2 OR |  |  |  |  |  |  |

| 0                                 | 1 | over voltage of half-bridge 1 and 2        |  |  |  |  |  |  |

| 1                                 | 0 | over temperature of half-bridge 3 and 4 OR |  |  |  |  |  |  |

| 1                                 | 0 | over voltage of half-bridge 3 and 4        |  |  |  |  |  |  |

| 0                                 | 0 | over temperature of all half-bridges OR    |  |  |  |  |  |  |

| 0                                 | 0 | over voltage of all half-bridge            |  |  |  |  |  |  |

**Pin Configuration**

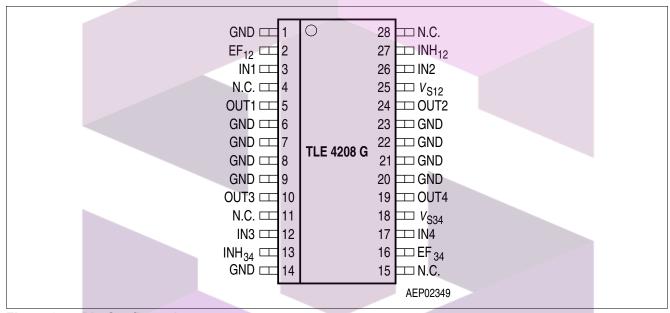

# 3 Pin Configuration

# 3.1 Pin Assignment

Figure 2 Pin Configuration

### 3.2 Pin Definitions and Functions

| Pin                              | Symbol            | Function                                                                             |

|----------------------------------|-------------------|--------------------------------------------------------------------------------------|

| 1, 6, 7,<br>8, 9, 14,<br>20, 21, | GND               | Ground; negative reference potential for blocking capacitor                          |

| 22, 23                           |                   |                                                                                      |

| 2                                | EF <sub>12</sub>  | Error Flag output of half-bridges 1 and 2; open collector; low = error               |

| 3                                | IN1               | Input channel of half-bridge 1; controls OUT 1                                       |

| 4, 11,<br>15, 28                 | N.C.              | Not Connected                                                                        |

| 5                                | OUT 1             | Power output of half-bridge 1; short circuit protected; with integrated clamp diodes |

| 10                               | OUT 3             | Power output of half-bridge 3; short circuit protected; with integrated clamp diodes |

| 12                               | IN3               | Input channel of half-bridge 3; controls OUT 3                                       |

| 13                               | INH <sub>34</sub> | Inhibit input of half-bridges 3 and 4; low = half-bridges 3 and 4 in stand-by        |

# **Pin Configuration**

| Pin | Symbol            | Function                                                                                          |  |  |  |  |  |

|-----|-------------------|---------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 16  | EF <sub>34</sub>  | Error Flag output of half-bridges 3 and 4; open collector; low = error                            |  |  |  |  |  |

| 17  | IN4               | Input channel of half-bridge 4; controls OUT 4                                                    |  |  |  |  |  |

| 18  | V <sub>S34</sub>  | Power supply voltage of half-bridges 3 and 4; positive reference potential for blocking capacitor |  |  |  |  |  |

| 19  | OUT 4             | Power output of half-bridge 4; short circuit protected; with integrated clamp diodes              |  |  |  |  |  |

| 24  | OUT 2             | Power-output of half-bridge 2; short circuit protected; with integrated clamp diodes              |  |  |  |  |  |

| 25  | V <sub>S12</sub>  | Power supply voltage of half-bridges 1 and 2; positive reference potential for blocking capacitor |  |  |  |  |  |

| 26  | IN4               | Input channel of half-bridge 4; controls OUT 2                                                    |  |  |  |  |  |

| 27  | INH <sub>12</sub> | Inhibit input of half-bridges 1 and 2;<br>low = half-bridges 1 and 2in stand-by                   |  |  |  |  |  |

# 4 General Product Characteristics

# 4.1 Absolute Maximum Ratings

#### Table 4 Absolute Maximum Ratings

$T_{\rm j}$  = -40°C to +150°; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                              | Symbol                    |              | Values | 3        | Unit | Note /                                    |

|----------------------------------------|---------------------------|--------------|--------|----------|------|-------------------------------------------|

|                                        |                           | Min.         | Тур.   | Max.     |      | Test Condition                            |

| Voltages                               |                           | <del>'</del> |        | <u> </u> |      |                                           |

| Supply Voltage                         | $V_{\rm S12},V_{\rm S34}$ | -0.3         | -      | 45       | V    | _                                         |

| Supply Voltage                         | $V_{\rm S12},V_{\rm S34}$ | -1           | _      | _        | V    | t < 0.5s;                                 |

|                                        |                           |              |        |          |      | $I_{S12}$ , $I_{S34} > -2A$               |

| Logic input voltages                   | $V_{I}$                   | -5           | _      | 20       | V    | ${\rm OV} < V_{\rm S12}, \ V_{\rm S34} <$ |

| (IN1; IN2; INH <sub>12</sub> ;         |                           |              |        |          |      | 45V                                       |

| IN3; IN4; INH <sub>34</sub> )          |                           |              |        |          |      |                                           |

| Logic output voltage                   | $V_{EF12},V_{EF34}$       | -0.3         | _      | 20       | V    | $0V < V_{\rm S12}, V_{\rm S34} <$         |

| (EF <sub>12</sub> ; EF <sub>34</sub> ) |                           |              |        |          |      | 45V                                       |

| Currents                               |                           |              |        |          |      |                                           |

| Output Current (cont.)                 | $I_{OUT1-4}$              | _            | -      | -        | Α    | internally limited                        |

| Output Current (peak)                  | $I_{OUT1-4}$              | -            | -      | _        | Α    | internally limited                        |

| Output Current (diode)                 | $I_{OUT1-4}$              | -1           | _      | 1        | Α    | -                                         |

| Output Current (EF)                    | I <sub>EF12-34</sub>      | -2           | _      | 5        | mA   | _                                         |

| Temperatures                           |                           |              |        |          |      |                                           |

| Junction Temperature                   | $T_{\rm j}$               | -40          | -      | 150      | °C   | _                                         |

| Storage Temperature                    | $T_{stg}$                 | -50          | -      | 150      | °C   | -                                         |

| Thermal Resistances                    |                           |              | ·      |          | ·    |                                           |

| Junction pin                           | $R_{ m thj\text{-}pin}$   | -            | -      | 25       | K/W  | measured to pin 7                         |

| Junction ambient                       | $R_{thjA}$                | _            | -      | 65       | kV   | -                                         |

#### **Notes**

- 1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

# 4.2 Functional Range

Table 5 Functional Range

| Parameter                                                     | Symbol                               | Symbol        |      | Values        |      | Note /                                                            |

|---------------------------------------------------------------|--------------------------------------|---------------|------|---------------|------|-------------------------------------------------------------------|

|                                                               |                                      | Min.          | Тур. | Max.          |      | Test Condition                                                    |

| Supply Voltage                                                | $V_{\mathrm{S12}}, V_{\mathrm{S34}}$ | $V_{UV\_OFF}$ | -    | 18            | V    | After $V_{\rm S12}$ , $V_{\rm S34}$ rising above $V_{\rm UV\_ON}$ |

| Extended Supply Voltage<br>Range for Operation                | $V_{\mathrm{S12}}, V_{\mathrm{S34}}$ | -0.3          | _    | $V_{UV\_ON}$  | V    | Outputs in tristate                                               |

| Supply Voltage transients slew rate                           | $V_{\mathrm{S12}}, V_{\mathrm{S34}}$ | -0.3          | _    | $V_{UV\_OFF}$ | V/µs | Outputs in tristate                                               |

| Logic input voltages<br>(IN1; IN2; INH12;<br>IN3; IN4; INH34) | $V_1$                                | -2            | -    | 18            | V    | -                                                                 |

| Junction Temperature                                          | $T_{j}$                              | -40           | _    | 150           | °C   | _                                                                 |

Note: Within the functional or operating range, the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the Electrical Characteristics table.

# 4.3 General Electrical Characteristics

## 4.3.1 Electrical Characteristics

### Table 6 Electrical Characteristics

$V_{\rm S12}$  =  $V_{\rm S34}$  = 8 V to 18 V, INH<sub>12</sub> = INH<sub>34</sub> = HIGH; I<sub>OUT1-4</sub> = 0A;  $T_{\rm j}$  = -40°C to +150°, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                                           | Symbol                              |                | Values                 |      |      | Note /                                                     |  |

|---------------------------------------------------------------------|-------------------------------------|----------------|------------------------|------|------|------------------------------------------------------------|--|

|                                                                     |                                     | Min. Ty        |                        | Max. |      | <b>Test Condition</b>                                      |  |

| Current Consumption                                                 |                                     | <u> </u>       |                        |      |      |                                                            |  |

| $INH_{12} = INH_{34} = LOW$                                         |                                     |                |                        |      |      |                                                            |  |

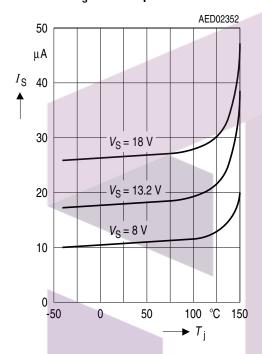

| Quiescent current                                                   | $I_{S}$                             | _              | _                      | 100  | μΑ   | $I_{\rm S} = I_{\rm S12} + I_{\rm S34}$                    |  |

| Quiescent current                                                   | $I_{S}$                             | -              | 20                     | 40   | μΑ   | $I_{\rm S} = I_{\rm S12} + I_{\rm S34};$                   |  |

|                                                                     |                                     |                |                        |      |      | $V_{S12} = V_{S34} = 13.2$<br>$T_i = 25  ^{\circ}\text{C}$ |  |

| INH <sub>12</sub> = HIGH and INH <sub>34</sub> = LOW                | or INH <sub>40</sub> = LOV          | │<br>V and INF | l <sub>or</sub> = HIGH |      |      | 1 <sub>j</sub> - 25 C                                      |  |

| Supply current                                                      | $I_{\rm S12}, I_{\rm S34}$          | _              | 10                     | 20   | mA   |                                                            |  |

| Supply current                                                      | I <sub>S12</sub> , I <sub>S34</sub> | _              | _                      | 30   | mA   | $I_{\text{OUT1/3}} = 0.4A$                                 |  |

| cappi, cament                                                       | 1512, 1534                          |                |                        |      | 1    | $I_{\text{OUT2/4}} = -0.4A$                                |  |

| Supply current                                                      | $I_{\rm S12}, I_{\rm S34}$          | _              | _                      | 50   | mA   | $I_{\text{OUT1/3}} = 0.8A$                                 |  |

|                                                                     |                                     |                |                        |      |      | $I_{\text{OUT2/4}} = -0.8A$                                |  |

| Over- and Under Voltage Locko                                       | out                                 |                |                        |      |      |                                                            |  |

| UV Switch ON voltage                                                | $V_{UVON}$                          | 7-             | 6.5                    | 7.5  | V    | $V_{\rm S12}, V_{\rm S34}$ increas                         |  |

| UV Switch OFF voltage                                               | $V_{UV\_OFF}$                       | 5              | 6                      | _    | V    | $V_{\rm S12}, V_{\rm S34}$ decreas                         |  |

| UV ON/ OFF hysteresis                                               | $V_{UV\_HY}$                        | -              | 0.5                    | _    | V    | V <sub>UV ON</sub> - V <sub>UV OFF</sub>                   |  |

| OV Switch OFF voltage                                               | $V_{OVOFF}$                         | _              | 20                     | 24   | V    | $V_{\rm S12}, V_{\rm S34}$ increas                         |  |

| OV Switch ON voltage                                                | $V_{OV\_ON}$                        | 18             | 19.5                   | _    | V    | $V_{\rm S12}, V_{\rm S34}$ decreas                         |  |

| OV ON/ OFF hysteresis                                               | $V_{OV\_HY}$                        | _              | 0.5                    | _    | V    | $V_{ m OVOFF}$ - $V_{ m OVON}$                             |  |

| Outputs OUT1; OUT2; OUT3; O                                         | UT4                                 |                |                        |      |      |                                                            |  |

| Saturation Voltages                                                 |                                     |                |                        |      |      |                                                            |  |

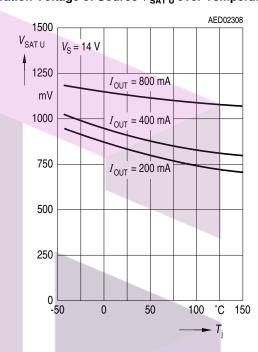

| Source (upper)                                                      | $V_{SAT\_U}$                        | -              | 0.85                   | 1.15 | V    | $T_{\rm j}$ = 25°C                                         |  |

| $I_{OUT12}$ , $I_{OUT34} = -0.2 \text{ A}$                          |                                     |                |                        |      |      |                                                            |  |

| Source (upper)                                                      | $V_{SAT\_U}$                        | -              | 0.90                   | 1.20 | V    | T <sub>j</sub> = 25°C                                      |  |

| $I_{OUT12}, I_{OUT34} = -0.4 \text{ A}$                             | 17                                  |                | 4.40                   | 4.50 | .,   | W. 0500                                                    |  |

| Sink (upper)                                                        | $V_{SAT\_U}$                        | -              | 1.10                   | 1.50 | V    | T <sub>j</sub> = 25°C                                      |  |

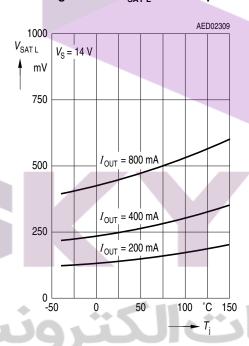

| $\frac{I_{OUT12}, I_{OUT34} = -0.8 \text{ A}}{\text{Sink (lower)}}$ | V                                   |                | 0.15                   | 0.23 | V    | <i>T</i> <sub>i</sub> = 25°C                               |  |

| $I_{OUT12}, I_{OUT34} = 0.2 A$                                      | $V_{SAT\_L}$                        | _              | 0.13                   | 0.23 | V    | 1 <sub>j</sub> - 25 C                                      |  |

| Sink (lower)                                                        | $V_{SAT\_L}$                        | 1 - 1          | 0.25                   | 0.40 | V    | <i>T</i> <sub>i</sub> = 25°C                               |  |

| $I_{OUT12}, I_{OUT34} = 0.4 \text{ A}$                              | · SAI_L                             |                |                        | 2    | 1 10 | لمولد                                                      |  |

| Sink (lower)                                                        | $V_{SAT\_L}$                        | _              | 0.45                   | 0.75 | V    | T <sub>i</sub> = 25°C                                      |  |

| $I_{OUT12}$ , $I_{OUT34} = 0.8 A$                                   | 5, 11_E                             |                |                        |      |      | ,                                                          |  |

|                                                                     |                                     |                |                        |      |      |                                                            |  |

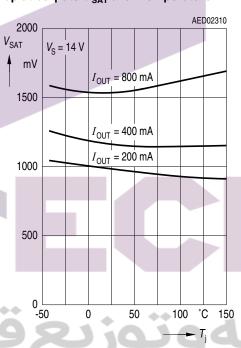

| Total Drop                                                          | $V_{SAT}$                           | -              | 1                      | 1.4  | V    | $V_{\text{SAT}} = V_{\text{SAT\_U}} + V_{\text{SAT\_U}}$   |  |

| $I_{OUT12}$ , $I_{OUT34} = 0.2 A$                                   |                                     |                |                        |      |      |                                                            |  |

### Table 6 Electrical Characteristics

$V_{\rm S12}$  =  $V_{\rm S34}$  = 8 V to 18 V, INH<sub>12</sub> = INH<sub>34</sub> = HIGH; I<sub>OUT1-4</sub> = 0A;  $T_{\rm j}$  = -40°C to +150°, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                                         | Symbol                      |      | Values |      |    | Note /                                                   |  |

|-------------------------------------------------------------------|-----------------------------|------|--------|------|----|----------------------------------------------------------|--|

|                                                                   |                             | Min. | Тур.   | Max. |    | <b>Test Condition</b>                                    |  |

| <b>Total Drop</b> I <sub>OUT12</sub> , I <sub>OUT34</sub> = 0.4 A | $V_{SAT}$                   | -    | 1.2    | 1.7  | V  | $V_{\text{SAT}} = V_{\text{SAT\_U}} + V_{\text{SAT\_L}}$ |  |

| <b>Total Drop</b> I <sub>OUT12</sub> , I <sub>OUT34</sub> = 0.8 A | $V_{SAT}$                   | -    | 1.6    | 2.5  | V  | $V_{\text{SAT}} = V_{\text{SAT\_U}} + V_{\text{SAT\_L}}$ |  |

| Clamp Diodes                                                      |                             |      |        |      |    |                                                          |  |

| Forward voltage; upper                                            | $V_{\sf FU}$                | _    | 1      | 1.5  | V  | $I_{F} = 0.4A$                                           |  |

| Upper leakage current                                             | $I_{LKU}$                   | _    | _      | 5    | mA | $I_{\rm F} = 0.4 {\rm A}^{1)}$                           |  |

| Forward voltage; lower                                            | $V_{FL}$                    | _    | 0.9    | 1.4  | V  | $I_{F} = 0.4A$                                           |  |

| Input Interface<br>Logic Inputs IN1; IN2; IN3; IN4                |                             |      |        |      | ·  |                                                          |  |

| H-input voltage                                                   | $V_{IH}$                    | _    | 2.0    | 3.0  | V  | _                                                        |  |

| L-input voltage                                                   | $V_{IL}$                    | 1.0  | 1.5    | _    | V  | -                                                        |  |

| Hysteresis of input voltage                                       | $V_{IHY}$                   | _    | 0.5    | _    | V  | -                                                        |  |

| H-input current                                                   | $I_{IH}$                    | -2   | _      | 10   | μΑ | V <sub>I</sub> = 5V                                      |  |

| L-input current                                                   | $I_{IL}$                    | -100 | -20    | -5   | μΑ | $V_{\rm I}$ = 0V                                         |  |

| Logic Inputs INH <sub>12</sub> ; INH <sub>34</sub>                |                             |      |        |      |    |                                                          |  |

| H-input voltage                                                   | $V_{IH}$                    | -    | 2.7    | 3.5  | V  | _                                                        |  |

| L-input voltage                                                   | $V_{IL}$                    | 1.0  | 2.0    | _    | V  | _                                                        |  |

| Hysteresis of input voltage                                       | $V_{IHY}$                   | -    | 0.7    | _    | V  | -                                                        |  |

| H-input current                                                   | $I_{IH}$                    | _    | 100    | 250  | μΑ | $V_{\rm INH}$ = 5V                                       |  |

| L-input current                                                   | $I_{IL}$                    | -10  | _      | 10   | μΑ | $V_{INH} = OV$                                           |  |

| Error Flags EF <sub>12</sub> ; EF <sub>34</sub>                   |                             |      |        |      |    | •                                                        |  |

| L-output voltage level                                            | $V_{EFL}$                   | _    | 0.2    | 0.4  | V  | $I_{EF}$ = 2 mA                                          |  |

| Leakage current                                                   | $I_{EFLK}$                  | _    | _      | 10   | μΑ | 0V < V <sub>EF</sub> < 7V                                |  |

| Thermal Shutdown                                                  |                             |      |        |      |    |                                                          |  |

| Thermal shutdown junction temperature                             | $T_{jSD}$                   | 150  | 175    | 200  | °C |                                                          |  |

| Thermal switch-on junction temperature                            | $T_{jSO}$                   | 120  | -      | 170  | °C |                                                          |  |

| Temperature hysteresis                                            | $\Delta T$                  | _    | 30     | _    | K  | _                                                        |  |

| 1) Not subject to production test, on                             | a aifia al lavo al a ai ava |      |        |      |    | I .                                                      |  |

<sup>1)</sup> Not subject to production test, specified by design

Data Sheet 11 Rev. 1.4, 2016-02-02

**Application Information**

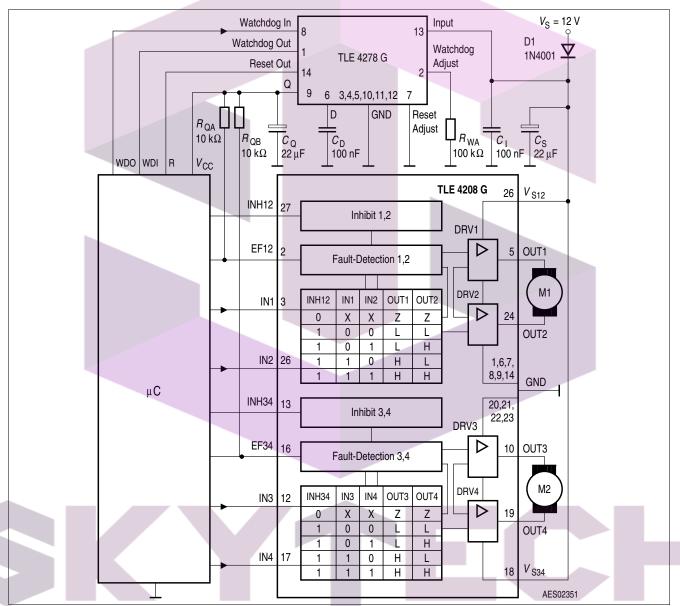

# 5 Application Information

Note: The following information is given as a hint for the implementation of the device only and shall not be regarded as a description or warranty of a certain functionality, condition or quality of the device.

Figure 3 Application Circuit 1 (Device is used as Dual-Full-Bridge-Driver)

Note: This is a very simplified example of an application circuit. The function must be verified in the real application.

### **Application Information**

# **Diagrams**

# Quiescent current $I_{\rm S}$ over Temperature

# Saturation Voltage of Source $V_{\mathrm{SAT}\,\mathrm{U}}$ over Temperature

Saturation Voltage of Sink  $V_{\mathsf{SATL}}$  over Temperature

Total Drop at outputs  $V_{\mathsf{SAT}}$  over Temperature

**Package Outlines**

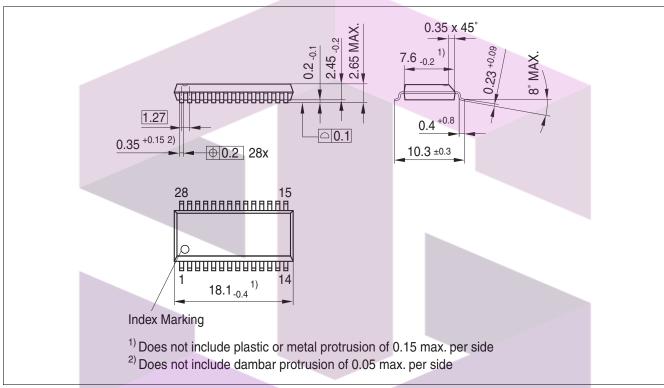

# 6 Package Outlines

Figure 4 PG-DSO-28

#### **Green Product (RoHS compliant)**

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations the device is available as a green product. Green products are RoHS-Compliant (i.e Pb-free finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020).

For further information on alternative packages, please visit our website: <a href="http://www.infineon.com/packages">http://www.infineon.com/packages</a>.

Dimensions in mm

**Revision History**

# 7 Revision History

| Revision | Date       | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|----------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Rev. 1.4 | 2016-02-02 | Correction of typographical errors Page 10: VOFF_OFF and VOFF_ON are inverted. No change of the device behavior. Page 10,11: VS1, respectively VS2, renamed VS12 and VS34                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Rev. 1.3 | 2014-02-12 | Updated package designation and to latest data sheet formatting                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| Rev. 1.2 | 2011-04-11 | Updated package designation to reflect various production sites.                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| Rev. 1.1 | 2008-02-04 | Initial version of RoHS-compliant derivate of TLE4208G Page 1: added AEC certified statement Page 1 and 13: added RoHS compliance statement and Green product feature Page 1 and 3: Editorial change: deleted "fully" (The term "fully protected" often leads to misunderstandings as it is unclear with respect to which parameters). Page 1 and 14: Package changed to RoHS compliant version Page 15: added Revision History, updated Legal Disclaimer |  |  |  |  |  |

#### Edition 2016-02-02

Published by Infineon Technologies AG 81726 Munich, Germany © 2016 Infineon Technologies AG All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information: